## Sub-100 Nanometer Channel Length Ge/Si Nanowire Transistors with Potential for 2 THz Switching Speed

Yongjie Hu,<sup>†</sup> Jie Xiang,<sup>†,||</sup> Gengchiau Liang,<sup>‡</sup> Hao Yan,<sup>†</sup> and Charles M. Lieber\*,<sup>†,§</sup>

Department of Chemistry and Chemical Biology, Harvard University, Cambridge, Massachusetts 02138, Department of Electrical and Computer Engineering, National University of Singapore, Singapore, and School of Engineering and Applied Sciences, Harvard University, Cambridge, Massachusetts 02138

Received December 30, 2007; Revised Manuscript Received January 21, 2008

## ABSTRACT

Ge/Si core/shell nanowires (NWs) are attractive and flexible building blocks for nanoelectronics ranging from field-effect transistors (FETs) to low-temperature quantum devices. Here we report the first studies of the size-dependent performance limits of Ge/Si NWFETs in the sub-100 nm channel length regime. Metallic nanoscale electrical contacts were made and used to define sub-100 nm Ge/Si channels by controlled solid-state conversion of Ge/Si NWs to NiSi<sub>x</sub>Ge<sub>y</sub> alloys. Electrical transport measurements and modeling studies demonstrate that the nanoscale metallic contacts overcome deleterious short-channel effects present in lithographically defined sub-100 nm channels. Data acquired on 70 and 40 nm channel length Ge/Si NWFETs with a drain—source bias of 0.5 V yield transconductance values of 78 and 91  $\mu$ S, respectively, and maximum on-currents of 121 and 152  $\mu$ A. The scaled transconductance and on-current values for a gate and bias voltage window of 0.5 V were 6.2 mS/ $\mu$ m and 2.1 mA/ $\mu$ m, respectively, for the 40 nm device and exceed the best reported values for planar Si and NW p-type FETs. In addition, analysis of the intrinsic switching delay shows that terahertz intrinsic operation speed is possible when channel length is reduced to 70 nm and that an intrinsic delay of 0.5 ps is achievable in our 40 nm device. Comparison of the experimental data with simulations based on a semiclassical, ballistic transport model suggests that these sub-100 nm Ge/Si NWFETs with integrated high- $\kappa$  gate dielectric operate near the ballistic limit.

There exist a growing number of challenges<sup>1</sup> associated with continuation of the remarkable scaling in performance and density of planar FETs achieved in the semiconductor industry over the past several decades due to physical and technical limitations of current device structures.<sup>2,3</sup> To overcome these issues, many researchers have been exploring chemically synthesized nanostructures, including semiconducting NWs and carbon nanotubes (CNTs). Researchers have shown that NW and CNT building blocks can be configured as p-type and n-type FETs and also used to "build" small logic circuits.<sup>4-6</sup> Moreover, there have been efforts addressing fundamental performance limits of CNT and NW FETs. CNT FETs with sub-100 nm channel lengths and performance exceeding p-type planar metal-oxidesemiconductor FETs (MOSFETs) have been reported.<sup>7a-c</sup> and analysis of data has shown that these devices operate near the ballistic limit.7d,e These advances demonstrate the promise

<sup>†</sup> Department of Chemistry and Chemical Biology, Harvard University. <sup>‡</sup> Department of Electrical and Computer Engineering, National University of Singapore. of CNT FETs, although development of CNT FET-based nanoelectronics will require advances in the production of uniform, semiconducting material versus mixtures of metallic and semiconductor CNTs.

Semiconductor NWs can be prepared with uniform and rationally controlled electronic properties in high yield<sup>4,5</sup> and thus offer substantial potential for exploring bottom-up approaches to nanoelectronic circuits, quantum devices, nanophotonics, and biological detectors.<sup>8</sup> An interesting example of our ability to "design" nanostructure electronic properties comes from emerging studies of Ge/Si core/shell NW heterostructures.<sup>9-11</sup> In particular, the structure of undoped Ge/Si NWs readily yields transparent contacts to a confined Ge conduction channel with a low-bias voltage mean-free-path on the order of hundreds of nanometers at room temperature,<sup>11a</sup> characteristics that are attractive for high-performance FETs<sup>10</sup> and low-temperature quantum devices.<sup>11b,c</sup> Indeed, previous studies of Ge/Si NWFETs with channel lengths from 1 to 0.2  $\mu$ m have shown scaled transconductance and on-current values that exceed substantially the performance of state-of-the-art Si MOSFETs.<sup>10,12</sup>

Critical tests of the true performance limits of Ge/Si NWFETs and comparison of these limits to other FET

<sup>\*</sup> Corresponding author. E-mail: cml@cmliris.harvard.edu.

<sup>&</sup>lt;sup>§</sup> School of Engineering and Applied Sciences, Harvard University.

<sup>&</sup>lt;sup>II</sup> Present address: Kavli Nanoscience Institute, California Institute of Technology, Pasadena, California, 91125.

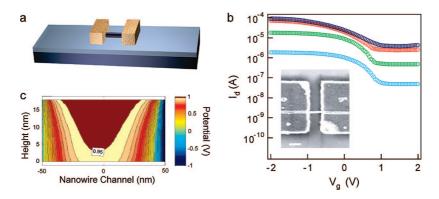

**Figure 1.** (a) Schematic of Ge/Si NW (dark blue) contacted with lithographically defined metal electrodes (gold). (b) Typical transport data from a 100 nm channel device with  $V_{ds} = -10$  mV and -0.1, -0.5, and -0.8 V, for cyan, green, red, and dark blue, respectively. Inset: scanning electron microscopy (SEM) image of a representative device. Scale bar is 100 nm. (c) Cross-section plot of the electrostatic potential from a 3D simulation at the off-state.<sup>15</sup> The plot is along the 100 nm NW channel (from -50 to 50 nm).

systems require studies of device scaling in the sub-100 nm channel length regime. A straightforward approach for testing this regime involves fabrication of NWFETs with  $\leq 100$  nm channels defined directly by lithography, as illustrated in Figure 1a.<sup>13</sup> The Ge/Si core/shell NWs used in these studies were synthesized by a two-step chemical vapor deposition process described previously.<sup>11a</sup> Top-gated devices were fabricated by electron-beam lithography.13 Typical transport data recorded on a 100 nm channel length device (Figure 1b) shows several important features. First, a large on-state current of ~0.1 mA was observed with a drain-source bias voltage  $(V_{ds})$  of -0.8 V. The large drive current is consistent with excellent transport characteristics of Ge/Si NWs and the small channel length. Second, the off-current of 4  $\mu$ A is quite large and limits the maximum on/off ratio to only 25. Third, even as  $V_{ds}$  is reduced further to 10 mV (Figure 1b), the off-state current, 50 nA, remains sizable.

Qualitatively, the large off-state current and small on/off ratio can be attributed to the electrostatic screening of gate coupling from the large lithography-defined contact electrodes<sup>14</sup> because the gate dielectric thickness, 4 nm, is much less than the channel length. To assess the validity of this suggestion, we performed 3-dimensional (3D) finite element simulations of the electrostatics of a NW device at the offstate.<sup>15</sup> Figure 1c shows a 2D cross-section plot of the electrostatic potential distribution inside a 100 nm Ge/Si NW channel along the axial direction with  $V_{\rm ds} = -1$  V and topgate bias  $V_{\rm g} = +1$  V. In the middle of the channel, the electrostatic potential is reduced to <0.95 V, smaller than the applied gate potential due to electric field lines terminating on the source/drain (S/D) electrodes. These results show that large S/D contact electrodes will screen the electrical field from the gate in short channels and thus limit gate voltage control at the off-state.

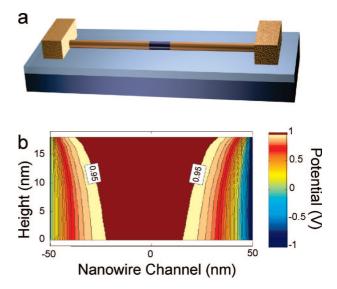

One approach to overcoming the unfavorable electrostatics would be to shrink substantially the size of the S/D electrodes.<sup>14</sup> We have evaluated this approach using 3D simulations described above<sup>15</sup> in the limit that the size of S/D contacts is the same as the NW diameter (Figure 2a). The simulations (Figure 2b) show that the electrostatic potential is close to the applied 1 V over a substantial portion of the channel. These results suggest that it should be possible

**Figure 2.** (a) Schematic of NW (dark blue) contacted with nanoscale electrodes (gold). (b) Plot of electrostatic potential distribution using conditions of Figure 1c, except that contact width and thickness are the same as the NW diameter.<sup>15</sup>

to achieve close to ideal gate coupling in the case where the S/D contacts are similar in size to the NWFET.

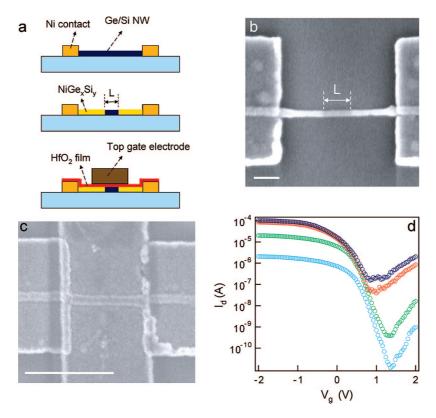

Previous studies have shown SiNWs can be transformed to silicide NWs<sup>16,17</sup> as well as partially converted to form metallic NiSi-Si-NiSi NW heterostructures by solid state reaction,16,18 thus yielding electrode structures similar to Figure 2a. We have developed a similar approach for the Ge/Si core/shell NWs to form NiGe<sub>x</sub>Si<sub>y</sub> NW contacts and subsequently deposit high-k HfO<sub>2</sub> dielectric and gate electrodes to complete the NWFETs, as illustrated in Figure 3a. To prepare the NiGe<sub>x</sub>Si<sub>y</sub>-Ge/Si-NiGe<sub>x</sub>Si<sub>y</sub> axial heterostructures, we (i) fabricate a longer channel device (0.5  $\mu$ m) by electron-beam lithography and then (ii) anneal the sample in consecutive steps, which leads to stepwise increases in the lengths of the NiGe<sub>x</sub>Si<sub>y</sub> NW regions and concomitant reductions in the Ge/Si NW channel length.<sup>19</sup> The stepwise annealing process was used to enable sufficient control of channel length in the sub-100 nm regime. Before top-gate fabrication, the Ge/Si channels were characterized by SEM (Figure 3b). These images show a clear contrast along the NW, with bright sections emerging from the Ni contacts,

**Figure 3.** (a) Schematic of the fabrication process for sub-100 nm channel Ge/Si NWFETs with nanoscale NiGe<sub>x</sub>Si<sub>y</sub> source/drain electrodes. (b) SEM image of a device before ALD deposition of HfO<sub>2</sub>. Scale bar is 100 nm. (c) SEM image of top-gated NWFET. Scale bar is 500 nm. (d) Transport data from a 100 nm channel length device, with cyan, green, red, and dark blue data corresponding to  $V_{ds} = -10 \text{ mV}$  and -0.1, -0.5, and -0.8 V, respectively.

which correspond to the metallic NiGe<sub>x</sub>Si<sub>y</sub>, and a dark segment sandwiched in between, which corresponds to the unreacted Ge/Si NW and taken as the effective channel length, *L*. The formation of metallic NiGe<sub>x</sub>Si<sub>y</sub> during device annealing was further confirmed by two-probe transport studies of completely transformed NWs (see Supporting Information Figure S1). Finally, top-gate structure was completed as shown in Figure 3c.<sup>13</sup>

Typical performance of a 100 nm channel length device prepared in this manner with NiGe<sub>x</sub>Si<sub>y</sub> NW S/D contacts is shown in Figure 3d. Significantly, the off-state current is reduced by a factor of 4000 for  $V_{ds} = -10$  mV for the device with nanoscale electrodes compared to lithographically defined 100 nm channel length devices (Figure 1b). The subthreshold slope is also improved to 140 mV/decade and shows no bias voltage dependence. In contrast, the subthreshold slope was bias voltage dependent and increased to above 1000 mV/decade at higher biases for the lithographically defined 100 nm channel length devices. These comparisons demonstrate that deleterious electrostatic screening effects were suppressed by scaling the contact size.

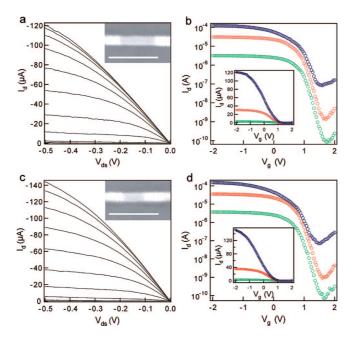

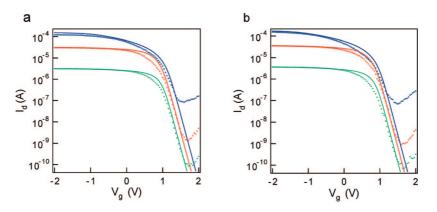

We have used this approach to fabricate and study NWFETs with sub-100 nm channels and show representative output and transfer characteristics for devices with channel lengths of 70 and 40 nm in Figure 4. The family of  $I_d-V_{ds}$  curves shows that the drain current,  $I_d$ , first increases and then saturates with increasingly negative drain voltage. Analysis of the transfer data for the 70 nm device (Figure 4b) yields a maximum drain current  $I_d(max)$  of 121  $\mu$ A at

$V_{\rm g} = -2$  V and a peak transconductance,  $g_{\rm m} = dI_d/dV_g$ , of 78  $\mu$ S at drain bias voltage  $V_{\rm ds} = -0.5$  V. Correspondingly, the data for the L = 40 nm device (Figure 4d) yields an  $I_{\rm d}({\rm max})$  of 152  $\mu$ A and  $g_{\rm m}$  of 91  $\mu$ S. The observed increases in  $I_{\rm d}({\rm max})$  and  $g_{\rm m}$  with decreasing channel length in these data is consistent with reduction in channel resistance as the device size is reduced.<sup>10</sup> We also note these  $I_{\rm d}({\rm max})$  and  $g_{\rm m}$  are the best values obtained to date in single semiconductor NW or CNT FETs.<sup>7,8a-f,10,20</sup>

These new data can be compared in a robust manner to longer channel Ge/Si NWFETs10 and state-of-the-art Si devices<sup>21</sup> by adopting the conventions used for planar devices.<sup>22</sup> First, the on and off current values are measured at  $V_{\text{g(on)}} = V_{\text{T}} - 0.7V_{\text{dd}}$  and  $V_{\text{g(off)}} = V_{\text{T}} + 0.3V_{\text{dd}}$ , where  $V_{\text{dd}}$ is the power supply voltage and  $V_{\rm T}$  is the threshold voltage. Second, the values are scaled to the device width,<sup>10</sup> where we use the total Ge core diameter  $D_{core}$  as the device width.<sup>23</sup> Comparison of the present data to longer channel Ge/Si NWFETs<sup>10</sup> shows improvements in scaled  $g_m$  and  $I_{on}$  for the 100 nm device (Table 1). The  $g_m$  values for 70 and 40 nm devices also exceed previous results for L = 190 nm (and 1  $\mu$ m) devices, although  $I_{on}$  remains lower as a result of the fact that  $V_{dd}$  is 50% of the value used in earlier device measurements. In addition, the L = 100, 70, and 40 nmchannel length devices exhibit values of the scaled  $I_{on}$  and gm that exceed state-of-the-art Si p-MOSFETs by factors of 2–3 and 5, respectively, even though a much smaller  $V_{dd}$  of 0.5–0.8 V was used in our study, compared to  $V_{dd} = 1.2$  V used in the MOSFET data. We attribute these latter perfor-

**Figure 4.** Transport characteristics of sub-100 nm channel length Ge/Si NWFETs. (a,c)  $I_d - V_{ds}$  data for L = 70 and 40 nm devices, respectively;  $V_g$  varies from -2 to 2 V in increments of 0.4 V from top to bottom. The insets show respective SEM images of the 70 and 40 nm devices; scale bars are 100 nm in both images. (b,d)  $I_d - V_g$  data for L = 70 and 40 nm devices, respectively. Insets show data on linear scale. The blue, red, and green data points correspond to  $V_{ds} = -10$ , -100, and -500 mV, respectively.

**Figure 5.** Length dependence of intrinsic delay is shown and compared with Si p-MOSFET results. Open circles represent data from ref 10. Solid squares are from this work. *C* was determined by numerical simulation<sup>10</sup> as  $C_{\rm L} = 800$  aF  $\mu m^{-1}$ .

mance improvements to a suppression of scattering in the clean quasi-one-dimensional Ge/Si NWs<sup>24</sup> and discuss this point further below.

Another important metric and point of comparison for FET performance is the intrinsic gate delay,  $\tau = CV/I$ , where C is the gate capacitance,  $V = V_{dd}$ , and I is on-current,  $I_{on}$ , as

defined by the  $V_{dd}$  window criteria discussed above. The intrinsic delay can be considered as the time scale for depletion of transistor gate charge CV at the on-state and therefore is an indication of how fast a transistor operates.<sup>3</sup> A summary of the results from 10 Ge/Si NWFETs versus L and the corresponding scaling for Si MOSFETs (Figure 5) highlights several key points. First, the scaling of  $\tau$  is more favorable for Ge/Si NWFETs than Si MOSFETs with a slope of  $\sim 1.5$  versus  $\sim 1.1$ . Second, the data show clear speed advantage at a given L for the Ge/Si NWFETs. For example, 1 THz switching speed ( $\tau = 1$  ps) is possible with L < 70nm versus ~30 nm for p-MOSFET.<sup>22</sup> Significantly, the 2 THz intrinsic speed indicated for the 40 nm device, represents the highest frequency among NWFETs and p-MOSFETs<sup>22</sup> and is comparable to the best value observed for CNT FETs.<sup>7a,22</sup> We note that it remains a challenge to verify such intrinsic behavior due to, for example, the effects of parasitic capacitance.

We have suggested that the excellent performance exhibited by the Ge/Si NWFETS can be attributed to a suppression of scattering in this quasi-one-dimensional system. One manner to evaluate this idea is to determine how close the NWFET operates to the scattering-free, ballistic limit.<sup>25</sup> We analyzed the performance of the L =70 and 40 nm Ge/Si NWFETs using a semiclassical,

| Table 1. Ge/Si NW | and MOSFET | Device | Comparison |

|-------------------|------------|--------|------------|

|-------------------|------------|--------|------------|

|                                                             |                                                    | Ge/Si NWFETs                                                                         |                                                                                    |                                                  |                                                       |

|-------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------|

|                                                             | $L = 190 \text{ nm}^a$<br>$(V_{dd} = 1 \text{ V})$ | $\begin{array}{l} L = 100 \text{ nm}^b \\ (V_{\rm dd} = \textbf{0.8 V}) \end{array}$ | $\begin{array}{l} L = 70 \text{ nm}^b\\ (V_{\rm dd} = \textbf{0.5 V}) \end{array}$ | $L = 40 \text{ nm}^b$ $(V_{dd} = 0.5 \text{ V})$ | $L = 35 \text{ nm}^c$<br>( $V_{dd} = 1.2 \text{ V}$ ) |

| $I_{\rm on}/D_{\rm core} ({\rm mA}/\mu{\rm m})$             | 2.5                                                | 3.3                                                                                  | 1.8                                                                                | 2.1                                              | 1.06                                                  |

| $g_{\rm m}/D_{\rm core}~({\rm mS}/\mu{\rm m})$              | 4.1                                                | 6.3                                                                                  | 5.3                                                                                | 6.2                                              | 1.32                                                  |

| <sup>a</sup> Ref 10. <sup>b</sup> This work. <sup>c</sup> ] | Ref 21.                                            |                                                                                      |                                                                                    |                                                  |                                                       |

**Figure 6.** (a,b) Comparison of simulated and measured transfer characteristics for 70 and 40 nm Ge/Si NWFETs, respectively. Symbols are experimental data, and solid lines are ballistic simulations. Green, red, and blue data points correspond to  $V_{ds} = -10, -100$ , and -500 mV, respectively. The significant deviation between measurements and simulations in the off-state are due to the ambipolar conduction and tunneling effects not included in the simulation.

ballistic transport model<sup>25,26</sup> coupled with a sp<sup>3</sup>d<sup>5</sup>s\* tightbinding model<sup>27</sup> to describe the electronic structure of Ge NW core.<sup>12,28</sup> Comparison of the calculated and experimental  $I_d - V_g$  transfer characteristics (Figure 6) shows very close agreement for low drain biases of  $V_{ds} = -10$  and -100 mV, which suggest that the experimental devices deliver dc current close to the ballistic limit. At a higher bias of  $V_{ds} =$ -0.5 V, the simulation results deviate from the experimental measurements,<sup>29</sup> which indicate the importance of inelastic scattering process such as high-field induced optical phonon scattering.<sup>30</sup> An estimate of the potential importance of these deviations was made by comparing the ratio of experimental and simulated on-currents at  $V_{\rm g} = -2$  V and  $V_{\rm ds} = -0.5$  V, which yields a value of ca. 80% and 90% for 70 and 40 nm devices, respectively. Thus we conclude that the sub-100 nm Ge/Si NWFETs operate very close to the ballistic limit.

In summary, we have described the first studies of the sizedependent performance limits of Ge/Si NWFETs in the sub-100 nm channel length regime. Metallic NiSi<sub>x</sub>Ge<sub>v</sub> NW electrical contacts were used to define sub-100 nm Ge/Si channels by controlled solid-state conversion of Ge/Si NW. Electrical transport measurements and modeling studies demonstrate that the nanoscale metallic contacts overcome deleterious short-channel effects present in lithographically defined sub-100 nm channels. Electrical transport data acquired on 70 and 40 nm channel length Ge/Si NWFETs yielded scaled transconductances of 5.3 and 6.2 mS/ $\mu$ m and scaled on-currents of 1.8 and 2.1 mA/µm, which exceed significantly the best reported values for planar p-Si MOS-FETs. In addition, analysis of the intrinsic switching delay shows that terahertz intrinsic operation speed is possible when channel length is reduced to 70 nm and that an intrinsic delay of 0.5 ps is achievable in our 40 nm device. Comparison of the experimental data with simulations based on a semiclassical, ballistic transport model suggests that these sub-100 nm Ge/Si NWFETs with integrated high- $\kappa$  gate dielectric operate very near the ballistic limit. The near ballistic transport in the Ge/Si NW short channel devices may open the door to ultrafast nanoelectronics based on the bottom-up concept<sup>4,31</sup> and could extend the roadmap for high-

Nano Lett., Vol. 8, No. 3, 2008

performance logic.<sup>1</sup>

Acknowledgment. We thank Professor Mark Lundstrom, Dr. Yue Wu, and Dr. Ying Fang for helpful discussions. C.M.L. acknowledges support of this work by Defense Advanced Research Projects Agency and Samsung Electronics Corporation.

**Supporting Information Available:** Two-probe current versus voltage curve for a 0.5  $\mu$ m long NiGe<sub>x</sub>Si<sub>y</sub> NW; current–voltage data recorded for a larger voltage range. This material is available free of charge via the Internet at http://pubs.acs.org.

## References

- International Technology Roadmap for Semiconductors, 2005 ed. and 2006 update; available online at http://public.itrs.net/.

- (2) (a) Lundstrom, M. Science 2003, 299, 210. (b) Haensch, W.; Nowak, E. J.; Dennard, R. H.; Solomon, P. M.; Bryant, A.; Dokumaci, O. H.; Kumar, A.; Wang, X.; Johnson, J. B.; Fischetti, M. V. *IBM J. Res. Dev.* 2006, 50, 339. (c) Barrett, C. R. MRS Bull. 2006, 31, 906.

- (3) (a) Sze, S. M. *Physics of Semiconductor Devices*, 2nd ed.; John Wiley & Sons Inc.: New York, 1981. (b) Taur, Y.; Ning, T. H. *Fundamentals of Modern VLSI Devices*; Cambridge University Press: Cambridge, UK, 1998.

- (4) (a) Lieber, C. M. MRS Bull. 2003, 28, 486. (b) Li, Y.; Qian, F.; Xiang, J.; Lieber, C. M. Mater. Today 2006, 9, 18. (c) Lu, W.; Lieber, C. M. J. Phys. D: Appl. Phys. 2006, 39, R387. (d) Lieber, C. M.; Wang, Z. L. MRS Bull. 2007, 32, 99.

- (5) (a) Xia, Y.; Yang, P.; Sun, Y.; Wu, Y.; Mayers, B.; Gates, B.; Yin, Y.; Kim, F.; Yan, H. Adv. Mater. 2003, 15, 353. (b) Wang, Z. L. Mater. Today 2004, 7, 26. (c) Yang, P. MRS Bull. 2005, 30, 85. (d) Thelander, C.; Agarwal, P.; Brongersma, S.; Eymery, J.; Feiner, L. F.; Forchel, A.; Scheffler, M.; Riess, W.; Ohlsson, B. J.; Gosele, U.; Samuelson, L. Mater. Today 2006, 9, 28.

- (6) (a) Dekker, C. *Phys. Today* **1999**, *52*, 22. (b) McEuen, P. L.; Fuhrer, M. S.; Park, H. *IEEE Trans. Nanotechnol.* **2002**, *1*, 78. (c) Avouris, Ph.; Chen, J. *Mater. Today* **2006**, *9*, 46. (d) Dai, H.; Javey, A.; Pop, E.; Mann, D.; Lu, Y. *NANO* **2006**, *1*, 1.

- (7) (a) Javey, A.; Guo, J.; Farmer, D. B.; Wang, Q.; Yenilmez, E.; Gordon, R. G.; Lundstrom, M.; Dai, H. *Nano Lett.* 2004, *4*, 1319. (b) Seidel, R. V.; Graham, A. P.; Kretz, J.; Rajasekharan, B.; Duesberg, G. S.; Liebau, M.; Uuger, E.; Kreupl, F.; Hoenlein, W. *Nano Lett.* 2005, *5*, 147. (c) Lin, Y.-M.; Appenzeller, J.; Chen, Z.; Chen, Z.-G.; Cheng, H.-M.; Avouris, Ph. *IEEE Electron Device Lett.* 2005, *26*, 823. (d) Javey, A.; Qi, P.; Wang, Q.; Dai, H. *Proc. Natl. Acad. Sci. U.S.A.* 2004, *101*, 13408. (e) Guo, J.; Javey, A.; Dai, H.; Lundstrom, M. *IEEE IEDM Tech. Dig.* 2004, 703.

- (8) (a) Cui, Y.; Zhong, Z.; Wang, D.; Wang, W. U.; Lieber, C. M. Nano Lett. 2003, 3, 149. (b) Zheng, G.; Lu, W.; Jin, S.; Lieber, C. M. Adv. Mater. 2004, 16, 1890. (c) Jin, S.; Whang, D.; McAlpine, M. C.;

Friedman, R. S.; Wu, Y.; Lieber, C. M. Nano Lett. 2004, 4, 915. (d) Friedman, R. S.; McAlpine, M. C.; Ricketts, D. S.; Ham, D.; Lieber, C. M. Nature 2005, 434, 1085. (e) Li, Y.; Xiang, J.; Qian, F.; Gradecak, S.; Wu, Y.; Yan, H.; Blom, D. A.; Lieber, C. M. Nano Lett. 2006, 6, 1468. (f) Jiang, X.; Xiong, Q.; Nam, S.; Qian, F.; Li, Y.; Lieber, C. M. Nano Lett. 2007, 7, 3214. (g) Javey, A.; Nam, S.; Friedman, R. S.; Yan, H.; Lieber, C. M. Nano Lett. 2007, 7, 773. (h) Zhong, Z.; Fang, Y.; Lu, W.; Lieber, C. M. Nano Lett. 2005, 5, 1143. (i) Yang, C.; Zhong, Z.; Lieber, C. M. Science 2005, 310, 1304. (j) Huang, Y.; Duan, X.; Lieber, C. M. Small 2005, 1, 142. (k) Qian, F.; Gradecak, S.; Li, Y.; Wen, C.; Lieber, C. M. Nano Lett. 2005, 5, 2287. (1) Cui, Y.; Wei, Q.; Park, H.; Lieber, C. M. Science 2001, 293, 1289. (m) Zheng, G.; Patolsky, F.; Cui, Y.; Wang, W. U.; Lieber, C. M. Nat. Biotechnol. 2005, 23, 1294. (n) Patolsky, F.; Timko, B. P.; Yu, G.; Fang, Y.; Breytak, A. B.; Zheng, G.; Lieber, C. M. Science 2006, 313. 1100.

- (9) Lauhon, L. J.; Gudiksen, M. S.; Wang, D.; Lieber, C. M. Nature 2002, 420, 57.

- (10) Xiang, J.; Lu, W.; Hu, Y.; Wu, Y.; Yan, H.; Lieber, C. M. Nature 2006, 441, 489.

- (11) (a) Lu, W.; Xiang, J.; Timko, B. P.; Wu, Y.; Lieber, C. M. *Proc. Natl. Acad. Sci. U.S.A.* **2005**, *102*, 10046. (b) Xiang, J.; Vidan, A.; Tinkham, M.; Westervelt, R. M.; Lieber, C. M. *Nat. Nanotechnol.* **2006**, *1*, 208. (c) Hu, Y.; Churchill, H. O. H.; Reilly, D. J.; Xiang, J.; Lieber, C. M.; Marcus, C. M. *Nat. Nanotechnol.* **2007**, *2*, 622.

- (12) Liang, G.; Xiang, J.; Kharche, N.; Klimeck, G.; Lieber, C. M.; Lundstrom, M. Nano Lett. 2007, 7, 642.

- (13) Epitaxial Ge/Si core/shell NWs with average core diameter of 14.6 nm, Si shell thickness of 1.7 nm, and  $\langle 110 \rangle$  core growth direction were prepared under the conditions described previously (ref 9, 10, 11a). Degenerately doped Si wafer with 600 nm thermal oxide was used as the substrate. Ni source/drain (S/D) contact electrodes (50 nm thickness) were defined by electron-beam lithography and thermal evaporation. Then the whole nanowire and contacts were covered by 4 nm HfO<sub>2</sub> using atomic layer deposition (ALD) process (ref 10). 35 cycles for HfO<sub>2</sub> deposition were used at 110 °C, with each cycle consisting of 1 s water vapor pulse, 5 s N<sub>2</sub> purge, 3 s precursor, and 5 s N<sub>2</sub> purge. Tetrakis(ethylmethylamino)hafnium [H<sub>f</sub>(N(CH<sub>3</sub>)(C<sub>2</sub>H<sub>5</sub>))<sub>4</sub>] was used as precursor. A second step of electron-beam lithography was used to define the top gate, followed by thermal evaporation of Cr/Au (5/50 nm).

- (14) Neophytou, N.; Guo, J.; Lundstrom, M. S. *IEEE Trans. Nanotechnol.* **2006**, *5*, 385.

- (15) The simulation was carried out using the program COMSOL Multiphysics and was simplified to consider electrostatic potential for the off-state. All parameters were based on the actual device: NW consists of 14.6 nm Ge (dielectric constant  $\kappa = 16$ ), and 1.7 nm Si ( $\kappa = 11.7$ ); electrode width is 600 nm and height is 50 nm; top-gate dielectric was treated as 4 nm half-surrounding HfO<sub>2</sub> with  $\kappa \sim 23$  (ref 10). Twodimensional plots in Figures 1c and 2b show potential distributions in the Ge core and Si dielectric shell.

- (16) Wu, Y.; Xiang, J.; Yang, C.; Lu, W.; Lieber, C. M. Nature 2004, 430, 61.

- (17) (a) Yamamoto, K.; Kohno, H.; Takeda, S.; Ichikawa, S. *Appl. Phys. Lett.* 2006, *89*, 083107. (b) Liu, B.; Wang, Y.; Dilts, S.; Mayer, T. S.; Mohney, S. E. *Nano Lett.* 2007, *7*, 818.

- (18) (a) Appenzeller, J.; Knoch, J.; Tutuc, E.; Reuter, M.; Guha, S. IEEE

*IEDM Tech. Dig.* **2006**, 1. (b) Weber, W. M.; Geelhaar, L.; Graham, A. P.; Unger, E.; Duesberg, G. S.; Liebau, M.; Pamler, W.; Cheze, C.; Riechert, H.; Lugli, P.; Kreupl, F. *Nano Lett.* **2006**, *6*, 2660. (c) Lu, K.-C.; Wu, W.-W.; Wu, H.-W.; Tanner, C. M.; Chang, J. P.; Chen, L. J.; Tu, K. N. *Nano Lett.* **2007**, *7*, 2389.

- (19) NiGe<sub>x</sub>Si<sub>y</sub>-Ge/Si-NiGe<sub>x</sub>Si<sub>y</sub> heterostructures were prepared as follows: Ge/Si NWFETs with Ni contacts separated by ~0.5 μm were fabricated (ref 13), loaded into a rapid thermal annealer (Heatpulse 610, Metron Technology), annealed in forming gas (N<sub>2</sub>:H<sub>2</sub> ratio, 90:10) at 300 °C with steps of 15 or 30 s, and a total annealing time (number of steps) was determined by monitoring the NW channel resistance change after each step.

- (20) (a) Wang, D. W.; Wang, Q.; Javey, A.; Tu, R.; Dai, H.; Kim, H.; McIntyre, P. C.; Krishnamohan, T.; Saraswat, K. C. *Appl. Phys. Lett.* 2003, 83, 2432. (b) Zhang, L.; Ryan, T.; Dai, H. *Nano Lett.* 2006, 6, 2785.

- (21) Ranade, R.; Ghani, T.; Kuhn, K.; Mistry, K.; Pae, S.; Shifren, L.; Stettler, M.; Tone, K.; Tyagi, S.; Bohr, M. *IEDM Tech. Dig.* **2005**, 4.

- (22) Chau, R.; Datta, S.; Doczy, M.; Doyle, B.; Jin, B.; Kavalieros, J.; Majumdar, A.; Metz, M.; Radosavljevic, M. *IEEE Trans. Nanotechnol.* 2005, *4*, 153.

- (23) Alternatively,  $I_{on}$  and  $g_m$  values can be calculated by scaling the electrostatic gate width,  $D_{core}*\pi/2$ , which corresponds to the half circumference of the NW channel in our top-gate device geometry. The scaled values of  $g_m$  and  $I_{on}$  for the 70 nm device are 3.4 mS  $\mu m^{-1}$  and 1.2 mA  $\mu m^{-1}$ , and 4.0 mS  $\mu m^{-1}$  and 1.3 mA  $\mu m^{-1}$ , respectively, for the 40 nm device. These values still exceed those of the state-of-the-art p-Si MOSFET.

- (24) Wang, J.; Polizzi, E.; Ghosh, A.; Datta, S.; Lundstrom, M. Appl. Phys. Lett. 2005, 87, 043101.

- (25) Rahman, A; Guo, J.; Datta, S.; Lundstrom, M. *IEEE Trans. Electron Devices* 2003, *50*, 1853.

- (26) Lundstrom, M.; Guo, J. Nanoscale Transistors: Device Physics, Modeling and Simulation; Springer: New York, 2005.

- (27) Boykin, T.; Klimeck, G.; Oyafuso, F. Phys. Rev. B 2004, 69, 115201.

- (28) We assume that the diameter and the gate capacitance of the Ge NW FET are 15 nm and 800 aF/ $\mu$ m (refs 10, 12). The series resistance  $R_{SD}$  is included on the model to be 2.5 and 3.3 k $\Omega$  for L=70 and 40 nm, respectively, as obtained from the experimental  $I_{ds}$  vs  $V_g$  characteristic at a low drain bias of  $V_D = 100$  or 10 mV. The Fermi level of the device at equilibrium is set to  $I_{off} = 1 \ \mu$ A at  $V_g = 1$  V for  $V_d = 0.1$  V. All of the values are satisfied by the extracted numbers from the experimental measurements.

- (29) The deviation of the threshold voltage between the experimental data and simulation data at high  $V_g$  can be attributed to the scattering mechanism. The back scattering will help carriers to fill up the negative *k* states and reduces the number of occupied subbands. Note that the number of charges in the device is determinate by the  $V_g$  at the device on-state. Therefore, the threshold voltage would be larger in the ballistic simulation than the actual device. Similar deviation is also observed in simulations for carbon nanotube devices (ref 7e).

- (30) Yao, Z.; Kane, C. L.; Dekker, C. Phys. Rev. Lett. 2000, 84, 2941.

- (31) Friedman, R. S.; McAlpine, M. C.; Ricketts, D. S.; Han, D.; Lieber, C. M. *Nature* **2005**, *434*, 1085.

NL073407B